#### ARQUITECTURA DE LOS SISTEMAS BASADOS EN MICROPROCESADOR

- Historia

- Bloques funcionales

- · Dimensionamiento

- Estructura CPU

- Concepto de programa

- Interrupciones

- Buses

- Memoria

- Entrada / Salida

- Ejemplo de arquitectura: Intel8086

- Ejemplo de sistema basado en μP: PC

FIG 1.4. Evolución de la informática

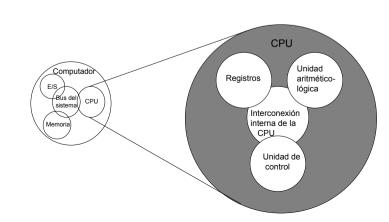

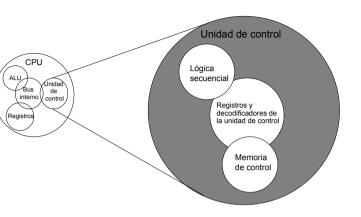

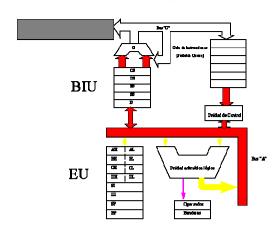

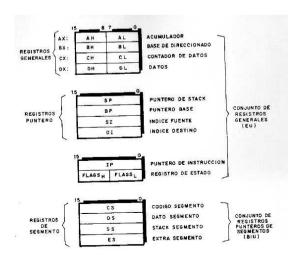

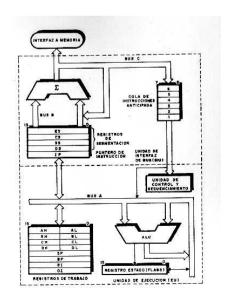

## Estructura de la CPU

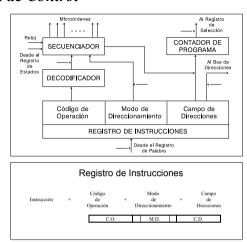

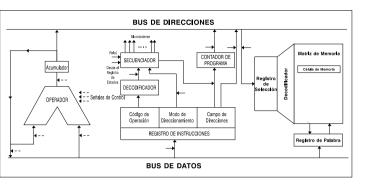

### Estructura de la unidad de control

#### Unidad de Control

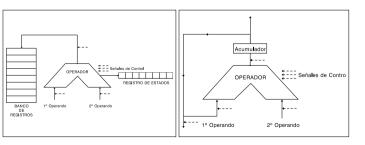

#### Unidad Aritmético-Lógica: ALU

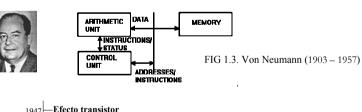

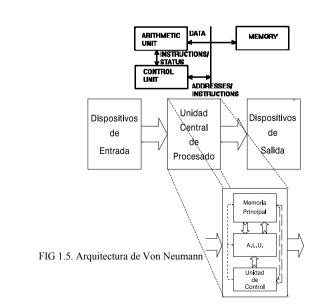

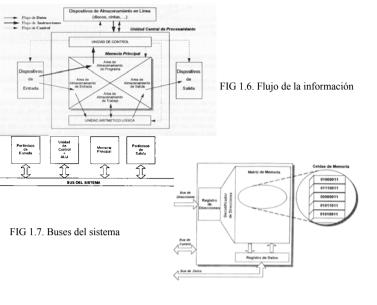

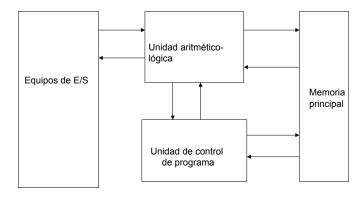

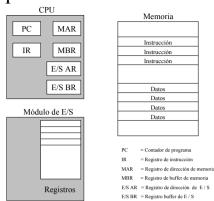

## Estructura de la máquina de von Neumann

#### Descripción General

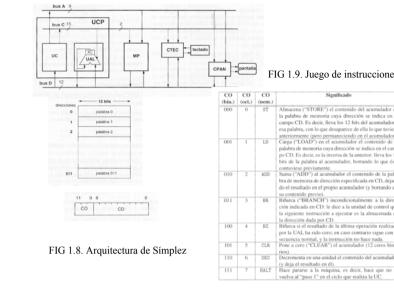

## Concepto del programa

- Los sistemas cableados no son flexibles.

- El harware de uso general puede realizar distintas funciones, según las señales de control aplicadas.

- En lugar de configurar el hardware, se proporciona un nuevo conjunto de señales de control.

# Componentes del computador: esquema de dos niveles

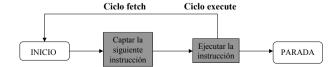

### Ciclo de instrucción básico

- Dos pasos:

- Fetch (Captación)

- Execute (Ejecución)

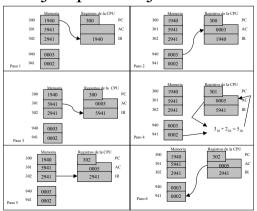

#### Ciclo fetch

- El contador de programa (PC) contiene la dirección de la instrucción que se debe captar a continuación.

- El procesador capta la instrucción que indica el PC desde la memoria

- El registro PC se incrementa,

- a no ser que se indique lo contrario.

- Esta instrucción se carga en el registro de instrucción (IR).

- El procesador interpreta la instrucción y lleva a cabo la acción requerida.

## Ejemplo de ejecución

#### Ciclo execute

- Procesador- memoria

- Transferencia de datos desde la CPU a la memoria.

- Procesador-E/S

- Transferencias de datos entre la CPU y un módulo de E/S.

- Procesamiento de datos

- Realización de alguna operación aritmética o lógica con los datos.

- Control

- Alteración de la secuencia de ejecución.

- Ejemplo: la instrucción de salto

- · Combinación de estas acciones

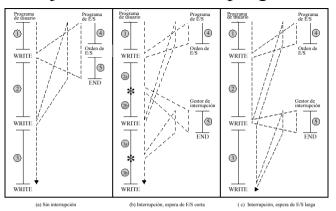

## Interrupciones

- Mecanismo mediante el que otros módulos (Ejemplo: E/S) pueden interrumpir el procesamiento normal de la CPU.

- Programa

- Ejemplo: desbordamiento aritmético ("overflow"), división por cero

- Temporización

- Generadas por un temporizador interno al procesador.

- Permite realizar ciertas funciones de manera regular.

- E/S

- Generadas por un controlador E/S.

- Fallo de hardware

- Ejemplo: error de paridad en la memoria

## Flujo de control de un programa

## Interrupciones múltiples

#### • Interrupciones inhabilitadas

- El procesador puede y debe ignorar la señal de petición de interrupción si se produce una interrupción en ese momento.

- La interrupción se mantiene pendiente y se examinará una vez se haya activado la primera interrupción.

- Las interrupciones se manejan en un orden secuencial estricto.

#### • Definir prioridades

- Una interrupción de prioridad más alta puede interrumpir a un gestor de interrupción de prioridad menor.

- Cuando se ha generado la interrupción de prioridad más alta, el procesador vuelve a la interrupción previa.

## Ciclo de interrupción

- · Añadido al ciclo de instrucción.

- El procesador comprueba si se ha generado alguna interrupción,

- indicada por la presencia de una señal de interrupción.

- Si no hay señales de interrupción, capta la siguiente instrucción.

- Si hay alguna interrupción pendiente:

- Se suspende la ejecución del programa en curso

- Guarda su contexto

- Carga el PC con la dirección de comienzo de una rutina de gestión de interrupción

- Proceso interrumpido

- Volver a almacenar el contexto y continuar con el programa interrumpido

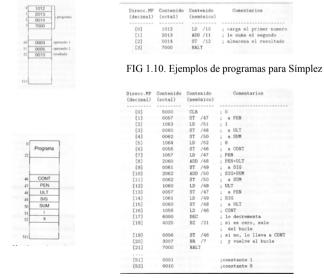

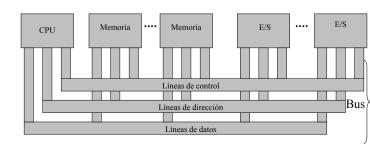

#### Buses

- Existe una serie de sistemas de interconexión.

- Las estructuras sencillas y múltiples son las más comunes.

- Ejemplo: control/dirección/bus de datos (PC)

- Es un medio de transmisión entre dos o más dispositivos.

- Suele constituirse en grupos:

- Un bus está constituido por varios caminos de comunicación, o líneas.

- Ejemplo: un dato de 8 bits puede transmitirse mediante ocho líneas del bus

#### Bus de datos

- Transmite datos.

- A este nivel no existe diferencia alguna entre "datos" y "instrucciones".

- La anchura del bus es un factor clave a la hora de determinar las prestaciones.

- 8, 16, 32, 64 bits.

#### Bus de control

- Información sobre señales de control y sobre temporización:

- Señal de escritura/lectura en memoria.

- Petición de interrupción.

- Señales de reloj.

#### Bus de dirección

- Designa la fuente o destino del dato.

- Ejemplo: cuando el procesador desea leer una palabra (datos) de una determinada parte en la memoria.

- La anchura del bus determina la máxima capacidad de memoria posible en el sistema.

- Ejemplo: 8080 tiene un bus de dirección de 16 bits, lo que supone 64k de espacio para direcciones

## Esquema de interconexión mediante un bus

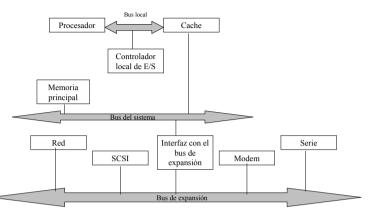

## Arquitectura de bus tradicional

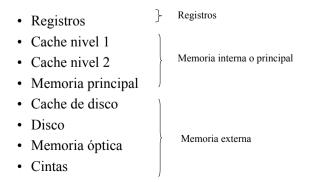

## Jerarquía de memoria

## Tipos de buses

- Dedicados

- Uso de líneas separadas para direcciones y para datos.

- Multiplexados

- Uso de las mismas líneas.

- Línea de control de dirección válida o de datos válida.

- Ventaja: uso de menos líneas.

- Desventajas:

- Se necesita una circuitería más compleja.

- · Posible reducción de las prestaciones.

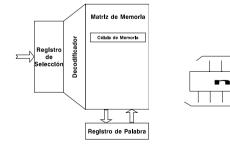

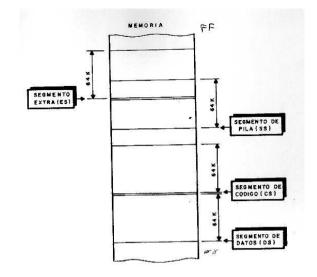

#### Memoria Principal - Organización Interna

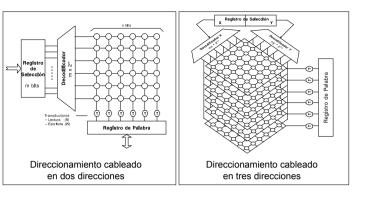

#### Memoria Principal - Direccionamiento

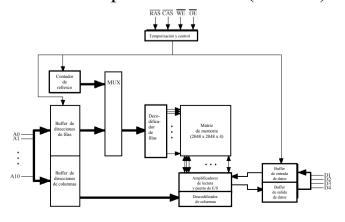

## DRAM típica de 16 Mb (4M x 4)

## Organización

- Un chip de 16Mbits podría estar estructurado en 1 Mpalabras de 16 bits.

- Un sistema de "un bit por chip" tiene 16 lotes de un chip de 1 Mbits, por lo que por cada chip corresponde 1bit de cada palabra y así, sucesivamente.

- Un chip de 16 Mbits puede estar estructurado en cuatro matrices cuadradas de 2048 x 2048 elementos

- Reduce el número de terminales de dirección.

- Direccionamiento de filas y de columna multiplexado.

- 11 terminales de dirección (2<sup>11</sup>=2.048).

- Una terminal más duplica el rango de los valores, así que la capacidad se multiplica por cuatro.

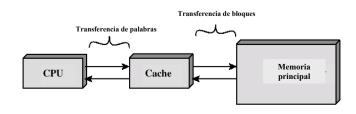

#### Cache

- Cantidad pequeña de memoria rápida.

- Está entre la memoria principal normal y la CPU.

- Puede localizarse en el chip o módulo de la CPU.

## Operación de la cache

- La CPU solicita contenidos de la localización de memoria.

- Comprueba la cache para estos datos.

- Si está, la obtiene de la cache (rápidamente).

- Si no está, lee el bloque requerido a partir de la memoria principal hasta la cache.

- Después, de la cache los entrega a la CPU.

- La cache incluye etiquetas para identificar qué bloque de la memoria principal está en cada ranura de la cache.

## E/S programada

- La CPU tiene control directo sobre la E/S

- Comprobación del estado del dispositivo

- Órdenes de lectura/escritura

- Transferencia de datos

- La CPU espera a que el módulo E/S acabe la operación

- Hace perder tiempo a la CPU

#### Técnicas de E/S

- Programada

- Mediante interrupciones

- Acesso directo a memoria (DMA)

## E/S mediante interrupciones

- La CPU no tiene que esperar.

- No se repite la comprobación del sistema.

- El módulo E/S envía una interrupción cuando está listo.

# Identificación del módulo que interrumpe (1)

- Diferentes líneas para cada módulo

- -PC

- Limita el número de dispositivos

- · Consulta software

- La CPU consulta a cada módulo

- Resulta lenta

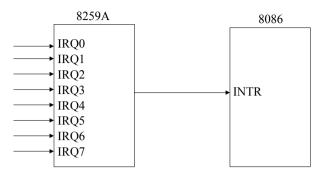

## Ejemplo: bus de PC

- El 80386 tiene sólo una línea de petición de interrupción.

- Los sistemas basados en el 80386 emplean un árbitro de interrupciones 82C59A.

- El 82C59A tiene 8 líneas de interrupción.

## Identificación del módulo que interrumpe (2)

- Conexión en cadena o consulta hardware

- La línea de reconocimiento de interrupción se conecta encadenando los módulos.

- El módulo que responde coloca un vector en el bus.

- La CPU emplea el vector para identificar la rutina de servicio.

- Arbitraje de bus

- El módulo debe disponer del control del bus antes de lograr la interrupción.

- Ej: bus PCI y puerto SCSI

### Secuencia de acontecimientos

- El 8259A acepta la interrupción.

- El 8259A determina la prioridad.

- El 8259A activa la señal 8086 (sitúa la señal INTR en la línea adecuada).

- El procesador reconoce la señal.

- El 8259A coloca el vector apropiado en el bus de datos.

- El procesador procesa la interrupción.

## Diseño de interrupción del PC

#### Funcionamiento del DMA

- Requiere un módulo adicional (hardware) en el bus

- El módulo del DMA obtiene el control de la CPU para transferir datos.

#### Acceso directo a memoria

- La E/S programada y con interupciones necesita la intervención directa de la CPU.

- La velocidad de transferencia es limitada.

- La CPU permanece ocupada mucho tiempo.

- El DMA es la solución.

#### Mecanismo del DMA

- La CPU envia una orden al módulo de DMA:

- Lectura/Escritura

- Dirección del dispositivo

- Dirección inicial de memoria para datos

- Cantidad de datos que hay que transferir

- La CPU continua con otro trabajo.

- El módulo del DMA realiza la transferencia.

- El módulo del DMA envía una señal de interrupción cuando ha acabado.

## Intel 8086

#### PC Alimentación Conectores Zócalo del micro teclado, ratón, USB... Conectores disco duro y disquetera Ranura AGP Ranuras PCI Ranuras

memoria

Ranuras

ISA